Our previous Blue Pearl post looked at the breadth of contextual visualization capability in the GUI to speed up debug. Two other important aspects of the ASIC & FPGA pre-synthesis workflow are automating analysis with scripts and managing the stream of messages produced. Let’s look at these aspects in the latest Blue Pearl 2016.1 release.

An important aspect to regression testing is to run exactly the same tests as a design is iterated. The solution is scripting, automating the types and sequence of analysis with a saved file for execution. Tcl is a powerful scripting language popular in EDA circles, and rather than stay with their own syntax Blue Pearl has chosen to migrate their tools entirely onto Tcl. However, instead of providing only a command line interface usually associated with Tcl, they’ve taken the idea farther.

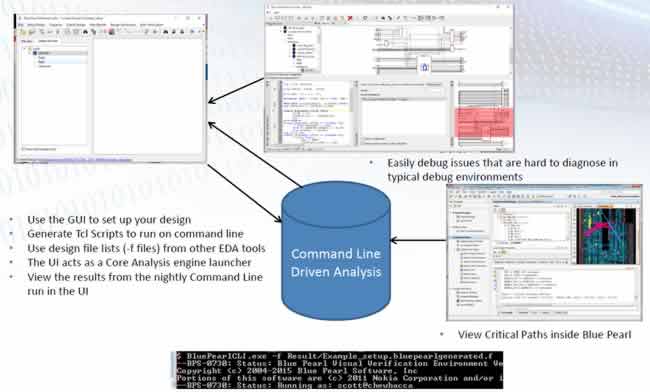

Both the GUI and the CLI are Tcl-based in the new release of the Blue Pearl suite. Set up can be done in the GUI and it can launch tests in the Core Analysis engine. For more complete test runs typically performed overnight, a Tcl script can be created and kicked off in the command line. Upon returning the next day, the CLI run can be loaded back into the GUI to allow the full visualization capability we discussed in our previous installment. This level of integration allows customized scripts for control, comparison of results from current and past runs, and rapid debug.

Those results are fundamentally a list of messages. With a well-designed message syntax, regular expressions can be used to process the list. In a sizable design with a long list of analysis messages, users will typically want to filter the list by different criteria. The Blue Pearl GUI allows some quick filtering capability via check boxes. More powerful message waiver capability now exists, including wild carding and string matching, which can be applied to a result set or removed – the results themselves are unmodified, only the managed view with waivers applied. This is handy where there are stylistic differences in code reviews; what one team considers a warning may be a mandatory fix for another.

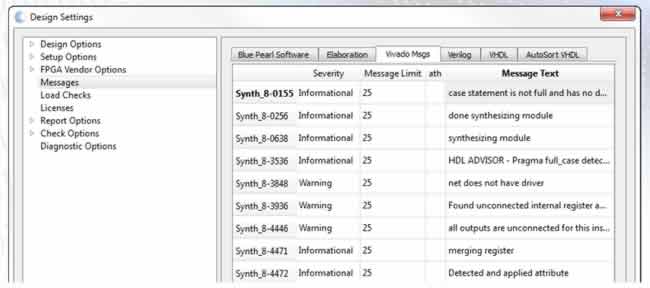

Messages can also be customized and grouped. Since the messages are stored in a SQL database – as are many other EDA tool messages – scripts can read text from other sources such as synthesis tools and add those messages into the Blue Pearl database. (Note in the image below the Xilinx Vivado messages have been incorporated.) The GUI can then sort, filter, waive, and compare messages accordingly. When developing with unique internal coding standards, this user-extendable capability is essential to ensuring consistency and efficiency.

Our focus in these Blue Pearl posts has been on usability of the tools rather than specifics of results in RTL and CDC analysis. The pre-synthesis checks Blue Pearl performs are extensive. Designers adopting these kinds of tools are generally not looking for something that generates a huge list of issues to sort through – they are looking for actionable items. The real need is tool that brings attention to the most urgent issues, and allows less interesting results to be kept in the background.

The idea behind “continuous integration” of chip designs is to provide a gate, a quality check difficult to implement with manual methods. The twist is that gate is not cleared once, but has to be cleared every time the design goes back for synthesis with any change. A process leveraging the Blue Pearl suite delivers more predictability in designs with automated checking and efficient debug.

Great news for ASIC & FPGA designers in their daily tasks, but what about that dreaded project review when engineers have to show management what is happening with the schedule? Next, we’ll explore what Blue Pearl is doing in the area of metrics, leading up to their big announcement at DAC in Austin.