Moore’s law foresaw the ability to pack twice as many transistors onto the same sliver of silicon every 18 months. Fast forward roughly 55 years, some experts now think Moore’s law is coming to an end. Others argue that the law continues with a blending of new innovations that leverage systemic complexity such as 2.5D and 3D integration techniques.

Moore’s law foresaw the ability to pack twice as many transistors onto the same sliver of silicon every 18 months. Fast forward roughly 55 years, some experts now think Moore’s law is coming to an end. Others argue that the law continues with a blending of new innovations that leverage systemic complexity such as 2.5D and 3D integration techniques.

FPGA vendors and their customers have taken advantage of Moore’s law for decades and reaped the benefits of innovations such as 2.5D interposer technology as well as hardened processors and application specific subsystems. However, with these features came new hardware design challenges. According to the 2020 Wilson Research study of FPGA designs:

- The FPGA market continues to struggle with non-trivial bug escapes into production

- The FPGA market is rapidly maturing its verification processes to address this growing complexity

- FPGA teams that are more mature in their functional verification methodology are likely to experience fewer bug escapes

As an example of this complexity, the study indicates that 92% of FPGA designs contain two or more asynchronous clock domain crossings (CDC). This class of metastability bugs cannot be found in RTL simulation. To simulate CDC issues requires a gate-level model with timing, which is often not available until late in the design flow, if at all. Even if such a gate-level model is available, it would still require a detailed set of test vectors to fully exercise the area of the circuit where the CDC exists, a daunting task at best.

The study also pointed out that 68% of designs miss their schedule! While there are several reasons for this, with static verification tools such Blue Pearl’s Visual Verification Suite, project teams avoid costly and time-consuming design spins due to simulation versus hardware mismatches, invalid timing constraints and CDC issues that can cause metastability problems.

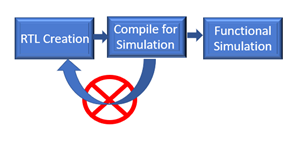

In addition, with static verification, 63% of trivial human errors or typostypically not found until simulation (sourceDVCon U.S. 2018) can instead be identified early as the design is being created. By “shifting verification left”, design teams have been proven to save time along with delivering on a much more predictable schedule.

In addition, with static verification, 63% of trivial human errors or typostypically not found until simulation (sourceDVCon U.S. 2018) can instead be identified early as the design is being created. By “shifting verification left”, design teams have been proven to save time along with delivering on a much more predictable schedule.

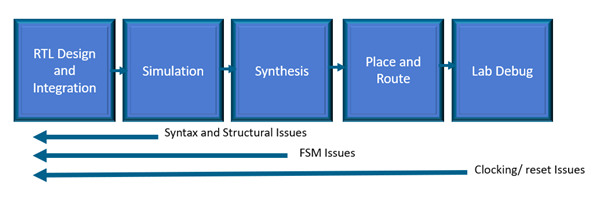

Mature RTL static verification tools such as Visual Verification Suite provide coding style conformance, structural, path, reset, and finite state machine analysis, as well as specific checks for DO-254 and STARC conformance.

FPGA teams that leverage static verification as part of their functional verification processes are proven to reduce expensive and time-consuming simulation, synthesis and place and routeruns and reruns, freeing up expensive licenses as well as improving overall design productivity.

As an example of the return on investment of adding static verification to an FPGA design methodology, let’s take an example of five FPGA designers working on a 12-month FPGA project. If each person worked 200 days per year, the project would take approximately 1000 person days. Let’s assume each designer spends about 50% of their time focused on one project that is 500 person days.

The Wilson study showed that approximately 51% of the design time is spent in simulation (250 person days). By adding static verification to the design methodology, if 50% (63% derated for simplicity) of the issues are trivial human errors or typos that can caught up front, this could save as much as 128 (250 x 51% x 50%) person days in simulation alone.

Next, if you add the impact of CDC issues, where ~37% of High Reliability designs have clock related issues, project teams could eliminate another possible 3 month delay due to additional simulation and/or lab debug to find a CDC issue, or 90 person days. Finally, if you add the project management efficiencies, the project team could save as much as 240 person days (1.2 person years).

To put this into real numbers, at a loaded cost of $150K/year/engineer, the net savings would be around $180K per year. This is not inclusive of other unratifiable savings, such as reduced simulation and synthesis license needs, project overrun costs/penalties, lab debug equipment and lab time as well as a significantly reduced risk of field failures. These savings far outweigh the costs of adding static verification as part of a complete functional verification methodology.

Whether you believe Moore’s law is coming to an end or not, one thing is clear: Most project teams are required to increase productivity just to keep up with FPGA complexity, often with smaller and smaller design teams. Blue Pearl’s Visual Verification Suite, used early and often in the design process as opposed to as an end of design/sign-off only tool, significantly contributes to design efficiency and quality, while minimizing chances of field failures.

To learn more about the Visual Verification suite, please request a demonstration.