A slogan is just that, a slogan or sometimes referred to as a tag line. Something catchy, something fresh and, of course, something we hope you don’t forget. So, with Blue Pearl Software’s slogan, ‘verify as you code’, we hope it conjures up a feeling that as you code, a smart editor is keeping watch. Making sure no mistakes sneak into the design, be it syntax, structural and even security issues.

So, what’s behind our slogan? Twenty-four years of technology to start with. Simply put, we have been helping HDL (VHDL / SystemVerilog) developers for quite some time. Over these years, we have refined the Visual Verification Suite to help FPGA and IP developers find critical issues up front in the design process, saving both time and money. We can honestly say, when you write code using the Visual Verification Suite’s HDL Creator smart editor, your HDL is verified as you code.

HDL Creator is ideal for developers coding both RTL and test benches who are seeking productivity, predictability and code quality for complex FPGAs and IP. HDL Creator provides real-time syntax and style code checking inside an intuitive, easy-to-use full featured editor. Unlike standard editors, HDL Creator provides advanced real-time file analysis to find and fix complex issues as you code, such as compilation dependencies and missing dependencies.

HDL Creator is a full-featured source code editor that provides all the normal features you would expect from a modern code editor such as autocomplete and error fix suggestions. HDL Creator provides over 2000 real time syntax and customer specific coding standard checks to streamline code development, saving time and effort all while averting common coding mistakes that could result in downstream design iterations. HDL Creator also provides advanced design views to help understand, verify, and debug as you code.

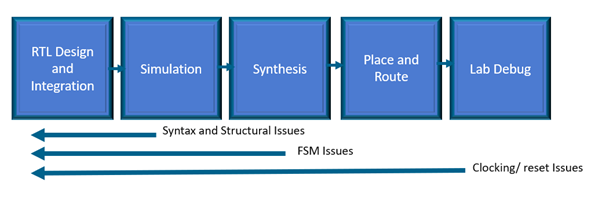

In addition to HDL Creator, the Visual Verification Suite also provides advanced static and formal RTL analysis to identify coding style and structural issues up front. While not real-time, like HDL Creator, the suite’s RTL Analysis points out 100’s of additional potential structural issues such as:

- Unnecessary events – These are unnecessary signals included in the sensitivity list. Such inclusion will lead to simulation mismatch and add complexity to achieving code coverage.

- If-Then-Else Depth – This will analyze the If-Then-Else structures to identify deep paths which may impact timing performance and throughput when implemented.

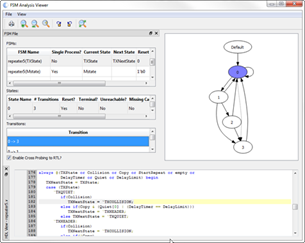

- Terminal State – This is a state in a state machine which once entered has no exit condition. Finding this prior to simulation can save wasted simulation time.

- Unreachable State – This is a state in a state machine which has no entrance condition. Finding this prior to simulation can again save considerable simulation time.

- Reset – This ensures each flip flop is reset and reset removal is synchronous to the clock domain of the reset. Several in-orbit issues have been detected relying upon the power-on status of registers and as such reset for all flip flops is best practice.

- Clocking – Clocking structures are also analyzed to ensure there is no clock gating or generation of internal clocks.

- Safe Counters – Checks counters to ensure that terminal counts use greater than or equal to for up counters and less than or equal to for down counters. This ensures single event effects have a reduced impact on locking up counters.

- Dead or unused code – Analyzes and warns about unused or dead code in the design. This can be removed prior to functional simulation and reduces head scratching when code coverage cannot be achieved.

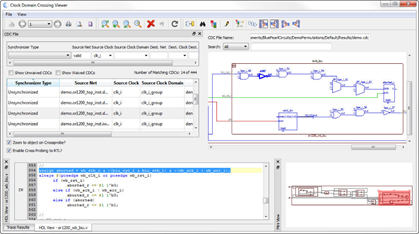

- Clock domain crossing – Ensuring clock domain crossing are synchronized to avoid metastability issues.

So, what is it that makes the Visual Verification Suite such a powerful debugging environment? It runs on Windows or Linux, and lets you easily move back and forth between command line mode and a straightforward, understandable graphical user interface. It can quickly generate reports that show aspects of your design in general, like your highest fanout nets, or your longest if-then-else chains, and an easy-to-filter report window showing the specific issues it has found. The suite also includes numerous checks to catch violations of company specific naming conventions.

Design teams that leverage static verification as part of their functional verification methodology are proven to reduce hardware security risks, as well as expensive and time-consuming simulation, synthesis and place and route runs and reruns, freeing up expensive licenses as well as improving overall design productivity.

Blue Pearl’s Visual Verification Suite, used early and often in the design process as opposed to as an end of design/sign-off only tool, significantly contributes to design security, efficiency, and quality, while minimizing chances of field vulnerabilities and failures.

We hope our slogan, ‘verify as you code’ comes to mind the next time you or your team develops an FPGA. To learn more, we encourage you to sign up for a demonstration to learn more how the Visual Verification Suite can ensure quality code for high reliability FPGAs.