Adam Taylor CEng FIET• 1stEmbedded Systems Consultant, FPGA Expert, Prolific FPGA Writer

A few weeks ago, we talked about how we could synchronise between clock domains in Vivado, I also noticed a couple of questions on r/FPGA about tools which could be used to find CDCs in designs. So, I thought it might be a good idea to blog about how we find CDC at Adiuvo Engineering and Training.

Of course, most vendor tools provide the ability to find CDCs in your design however, as they are not specialised for CDC the reports which are presented and debugging views can be a difficult to interpret. So just as vendors supplied simulation tools are often not used professionally opting for a higher performance simulation tool instead, it is common to use a third-party CDC tool.

Within Adiuvo we use Blue Pearls Visual Verification Suite to ensure our designs have no CDC issues. This works well for us as several of our clients including the European Space Agency use Visual Verification Suite for CDC and structural analysis.

One of the benefits of using VVS is that the analysis is conducted on the actual RTL therefore there is no need to wait for synthesis to complete before the analysis can be used. The tool is also vendor independent so we can use it to verify RTL designs that we might want to reuse across several vendors.

Let’s look at how we can find a CDC using VVS. Blue Pearl works in two stages, the first stage is loading in the design during which the RTL is checked using the Verific parser for LRM compliance. The design is also check for completeness e.g., are all the source files present and we do not have any missing blocks which would become black boxes and prevent the correct CDC analysis.

Once the design is loaded successfully, we can run the more detailed analysis options, one of these is CDC, the others are path analysis – identifying longest paths in the design and Multipath and False path identification.

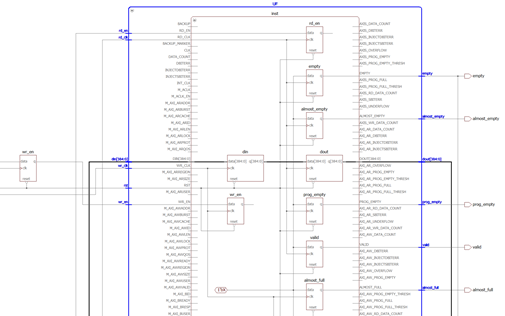

To be able to do CDC analysis we need to have informed the tool of which vendor we are using, VVS has built in vendor libraries which enables the CDC analysis to be formed on design including IP. VVS does this by creating what is known as grey cell for the IP being used the grey cell includes only the input and output rank of flip flops. Knowing the clock domains of the IO enables VVS to determine if a CDC has been introduced.

The CDC analysis itself takes only a few minutes to analysis the RTL and produce a list of potential CDC for the engineer to investigate.

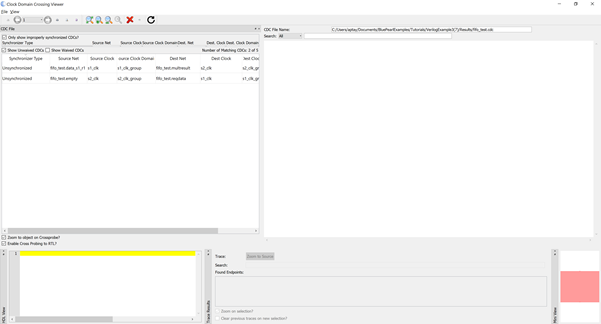

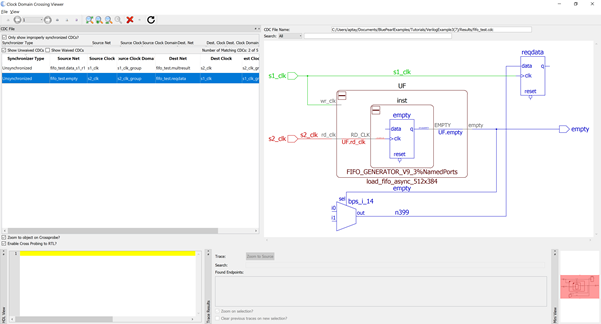

Clicking on the failing CDC path will cross probe not only to the source code but draw a schematic diagram which shows the failing path.

In the example above it shows the insertion accidently of a CDC as the FIFO empty signal is associated with the read clock, but it has been used with the write clock without appropriate clock domain crossing protection.

We find the visual analysis of the potential CDC and the cross probing to the source code very useful; it enables us to quickly home in on the area of code which might be a problem.

The reports are also very useful when it comes to gaining acceptance and sign off from clients as part of the design assurance process, as we can demonstrate the CDC checks have been performed.